#### America

Epson America, Inc. Headquarter:

3840 Kilroy Airport Way Long Beach, California 90806-2452 USA Phone: +1-562-290-4677

San Jose Office: 214 Devcon Drive San Jose, CA 95112 USA Phone: +1-800-228-3964 or +1-408-922-0200

#### Europe

Epson Europe Electronics GmbH Riesstrasse 15, 80992 Munich, Germany Phone: +49-89-14005-0 FAX: +49-89-14005-110

#### Asia

Epson (China) Co., Ltd. 4th, Floor, Tower 1 of China Central Place, 81 Jianguo Road, Chaoyang District, Beijing 100025 China Phone: +86-10-8522-1199 FAX: +86-10-8522-1120

Shanghai Branch Room 1701 & 1704, 17 Floor, Greenland Center II, 562 Dong An Road, Xu Hui District, Shanghai, China Phone: +86-21-5330-4888 FAX: +86-21-5423-4677

Shenzhen Branch Room 804-805, 8 Floor, Tower 2, Ali Center, No.3331 Keyuan South RD(Shenzhen bay), Nanshan District, Shenzhen 518054, China Phone: +86-10-3299-0588 FAX: +86-10-3299-0560

Epson Taiwan Technology & Trading Ltd. 15F., No.100, Songren Rd., Sinyi Dist., Taipei City 110. Taiwan Phone: +886-2-8786-6688

Epson Singapore Pte., Ltd. 1 HarbourFront Place, #03-02 HarbourFront Tower One, Singapore 098633 Phone: +65-6586-5500 FAX: +65-6271-3182

Seiko Epson Corp. Korea Office 19F, KLI 63 Bldg., 60 Yoido-dong, Youngdeungpo-Ku, Seoul 150-763, Korea Phone: +82-2-784-6027 FAX: +82-2-767-3677

Seiko Epson Corp. **Sales & Marketing Division**

#### **Device Sales & Marketing Department**

421-8, Hino, Hino-shi, Tokyo 191-8501, Japan Phone: +81-42-587-5816 FAX: +81-42-587-5116 ASICs Gate Arrays / Embedded Arrays / Standard Cells

Epson semiconductor website global.epson.com/products\_and\_drivers/semicon/

Document code : 701077824 First Issue April 2006 Revised March 2019 in JAPAN  $\oplus$

### 2019

## **Business Concept**

Expanding use of smartphones and tablets is giving broadband internet and wireless communications even greater roles in our daily lives, and making the arrival of the ubiquitous network society an inevitable reality. In particular, semiconductors for use in portable devices, information terminals, in-vehicle devices and FA devices are expected to provide higher performance in terms of thinner structure, lighter weight, and longer operation with limited power supply. We have been focusing on the creation of compact, lowpower semiconductors since we started the development of CMOS LSI for watches in 1969. Since then, we have steadily built up our expertise in energy-saving, space-saving, and time-saving designs. This has enabled us to quickly obtain the semiconductor development technology needed to meet the demands of the new era of ubiquitous networks. Our concept is to develop "saving technologies" to reduce power consumption, development times, and implementation space. Our goal is to be a true partner for you, providing you with strategic advantages, enhancing your customer value based on our "saving technologies" and mixed analog/ digital technologies that we have cultivated, as well as our design capabilities, manufacturing capabilities and stable supply that can satisfy your detailed requirements.

## **Environmental Responsibility**

Epson semiconductor technology provides environmental value to customers by creating and manufacturing eco-friendly products.

1) We Epson's products are surely complying with the Eu-RoHS (2011/65/EU) Directive.

- 2) We are releasing information about the containing chemical substances of products at web-site. Product of QFP & BGA are described in the following URL.

- global.epson.com/products and drivers/semicon/information/package lineup.html \*Some products are excluded.

- Environmental management system third party certification status

ISO14001

Type of certification : ISO 14001: 2015, JIS Q 14001: 2015 Awarded to : TOHOKU EPSON CORPORATION, SEIKO EPSON CORPORATION

(Fujimi Plant, Suwa Minami Plant) Certified by : Bureau Veritas Japan Co., Ltd.

Date of certification : April 3, 1999 Type of certification : ISO 14001: 2015

Awarded to : Singapore Epson Industrial Pte. Ltd. Certified by : SGS Date of certification : Jan 12, 1999

## **Epson's Quality Policy**

Keeping the customer in mind at all times, we make the guality of our products and services our highest priority. From the quality-assurance efforts of each employee to the quality of our company as a whole, we devote ourselves to creating products and services that please our customers and earn their trust. Epson has acquired ISO9001 and IATF16949 certification with its IC, module and their application products.

#### Quality Management system third party certification status ISO9001 Type of Certification : ISO9001: 2015 , JIS Q 9001: 2015 Awarded to : TOHOKU EPSON CORPORATION, SEIKO EPSON CORPORATION (Fujimi Plant, Suwa Minami Plant, Hino Office) Certified by : Bureau Veritas Japan Co., Ltd. Certificate No.: 3762381 Initial Date of Certification : October 10, 1993 Type of Certification : ISO9001: 2015 Awarded to : Singapore Epson Industrial Pte. Ltd. Certified by : SGS Certificate No. : SG03/00011 Initial Date of Certification : February 4, 2003 IATF16949 Type of Certification : IATF16949:2016 Awarded to : TOHOKU EPSON CORPORATION, SEIKO EPSON CORPORATION (Fujimi Plant, Suwa Minami Plant, Hino Office), EPSON EUROPE **ELECTRONICS** GmbH Certified by : Bureau Veritas Japan Co., Ltd. Certificate No. : 281371 Initial Date of Certification : Dec 9, 2017

Type of Certification : IATF16949:2016 Awarded to : Singapore Epson Industrial Pte. Ltd. Certified by : SGS Certificate No. : SG07/00021 Initial Date of Certification : May 2, 2018

#### 0 Ν Т E Ν

| History of Epson semiconductor | 4-5   |

|--------------------------------|-------|

|                                |       |

| ASIC Product Lineup            | 6-7   |

|                                |       |

| Gate Arrays                    | 8-9   |

|                                |       |

| Embedded Arrays                | 10    |

|                                |       |

| Standard Cells                 | 11    |

|                                |       |

| Macro Cells                    | 12-13 |

|                                |       |

| Epson Originals                | 14-16 |

|                                |       |

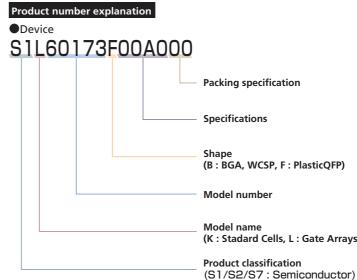

(B : BGA, WCSP, F : PlasticQFP)

(K : Stadard Cells, L : Gate Arrays, X : Embedded Arrays)

| Package Lineup                                                                                | 17-19 |

|-----------------------------------------------------------------------------------------------|-------|

| Gate Array Package List<br>Package's Thermal Resistance<br>Jser Interface<br>Development Flow |       |

| Gate Array Package List                                                                       | 20-22 |

|                                                                                               |       |

| Package's Thermal Resistance                                                                  | 23    |

|                                                                                               |       |

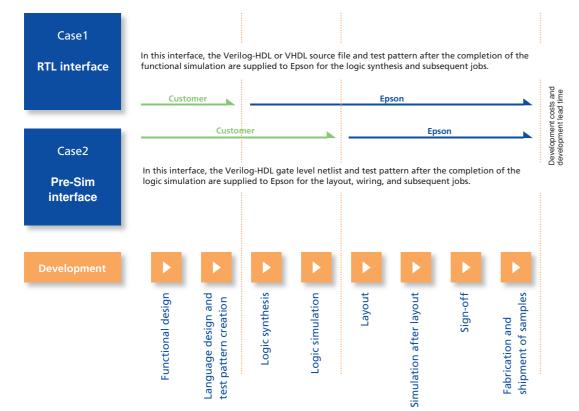

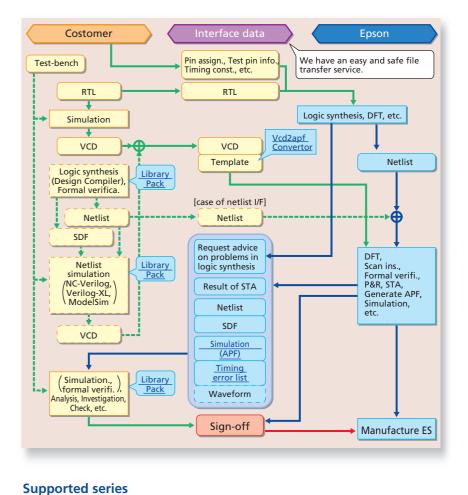

| User Interface                                                                                | 24    |

|                                                                                               |       |

| Development Flow                                                                              | 25    |

|                                                                                               |       |

| Epson ASIC Website                                                                            | 26    |

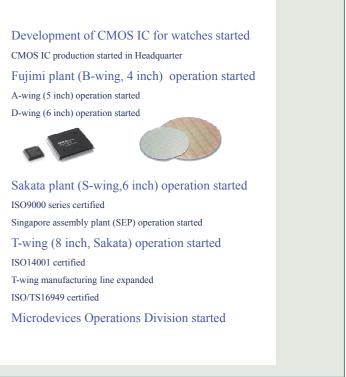

## History of Epson semiconductor **ASICs**

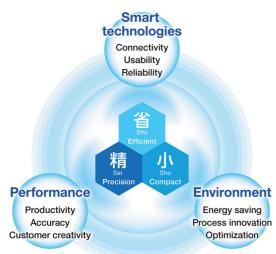

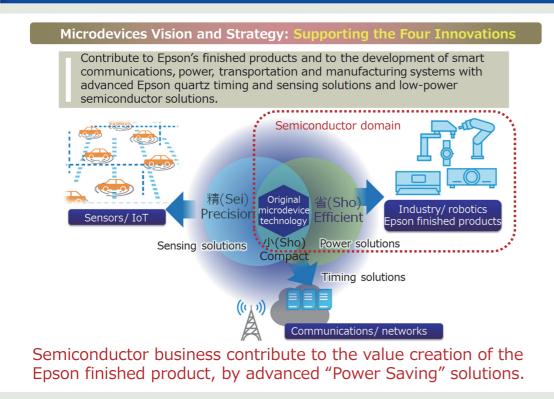

### Value Generated by Epson Technologies

Value generated by Epson's efficient, compact and precision technologies

#### Smart technologies

Create convenient and easy-to-use products that can be used anytime and anywhere, and which help customers reduce waste, and save effort, time and money.

#### Environment

Leverage Epson products to reduce environmental impact by improving customers' work processes, and contribute to a sustainable society.

#### Performance

Use outstanding products to contribute to customers' performance through productivity, accuracy and creativity.

### The role of Microdevices Div. and Semiconductor domain

# History of Epson semiconductor

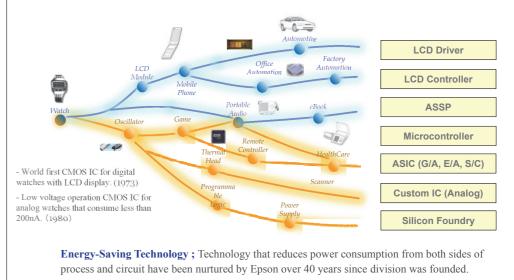

## History of Epson Semiconductor's Technology

As the semiconductor division of "worldwide watch maker Seiko", semiconductor business has expanded into LCD Drivers, ASICs and MCUs from IC for Watches. These businesses are all based on Epson's energy-saving technology.

### **Epson Semiconductor's History**

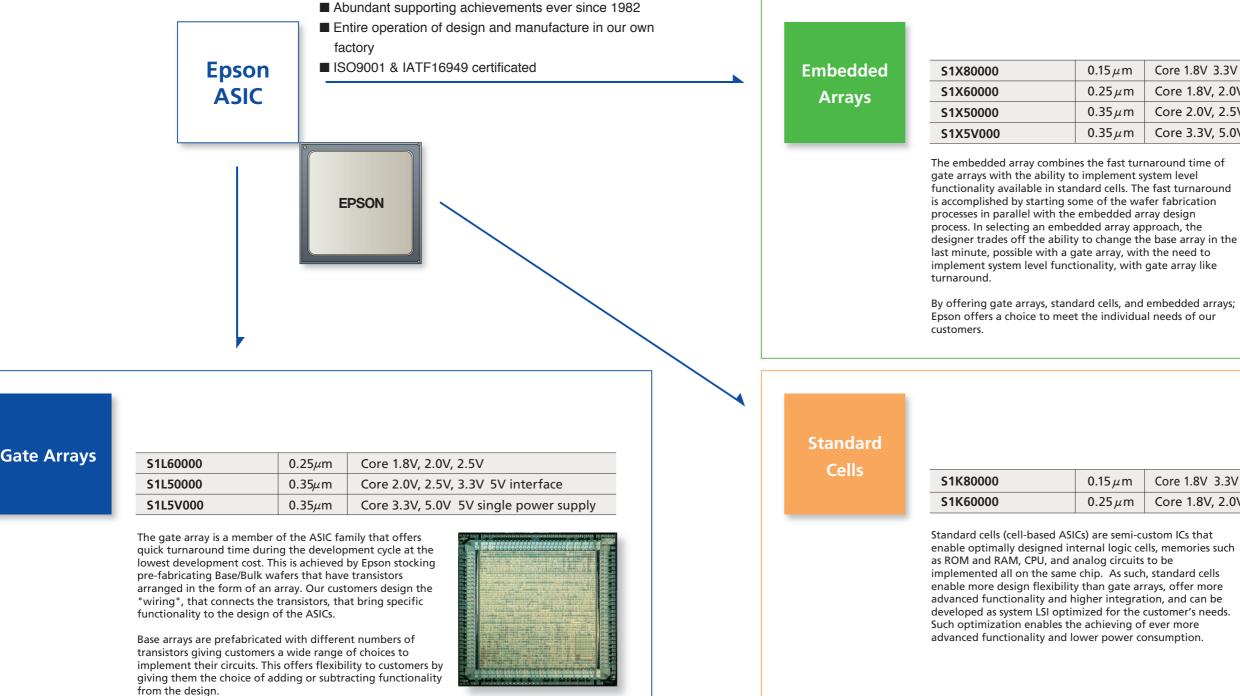

### **ASIC Product Lineup ASICs**

# **ASIC Product Lineup**

Epson's ASIC offerings aim to provide the best overall solution thus enabling our customers to get products to market successfully. Epson ASIC products include gate arrays that address the need for fast turnaround, at low IC development costs; Standard Cells, that make system solutions possible at the lowest unit price, and embedded arrays that combine the fast turnaround time of gate arrays with the ability to implement system level functionality on chips available with standard cells.

| m  | Core 1.8V 3.3V single power supply with LDO |

|----|---------------------------------------------|

| ιm | Core 1.8V, 2.0V, 2.5V 5V interface          |

| ιm | Core 2.0V, 2.5V, 3.3V 5V interface          |

| ιm | Core 3.3V, 5.0V 5V single power supply      |

|   | Core 1.8V 3.3V single power supply with LDO |

|---|---------------------------------------------|

| m | Core 1.8V, 2.0V, 2.5V 5V interface          |

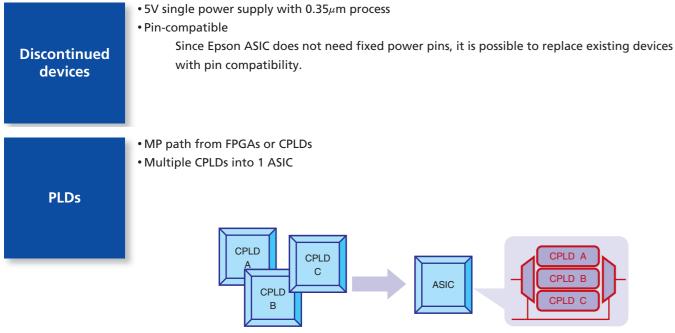

Epson's Gate Array is a suitable solution for replacing existing devices because this Gate Array option gives flexibility to adapt the power supply and layouts of other various signals. Furthermore Epson has invested on the new Gate Array series called "S1L5V000" which supports 5V single power supply with 0.35µm process. Since it is a new series, it is also suitable for long life time applications.

| S11 5000                                                  | O Sorioo        |                                                                                                   |             |              |             |                     |              |              |            |              |             |             |             | Core       | I/O      |   |

|-----------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------|-------------|--------------|-------------|---------------------|--------------|--------------|------------|--------------|-------------|-------------|-------------|------------|----------|---|

| SIL5000                                                   | 0 Series        |                                                                                                   |             |              |             |                     |              |              |            |              |             |             |             | 2.0V       | 2.0V     |   |

| Se                                                        | ries            | S1L50                                                                                             | 000 Seri    | es           |             |                     |              |              |            |              |             |             |             | 2.00       | 3.3V     |   |

|                                                           | • Ultra l       | • Ultra large scale integration (0.35 $\mu$ m CMOS, using 2-, 3- or 4-layer interconnect process) |             |              |             |                     |              |              |            |              | 2.5V        | 2.5V        |             |            |          |   |

|                                                           | • High-s        | peed oper                                                                                         | ration (0.1 | 4 ns delay   | / at 3.3 V, | with 2-inp          | out power    | r NAND Ty    | /p.)       |              |             |             | 2.50        | 3.3V       |          |   |

| Features                                                  |                 | • Low p                                                                                           | ower cons   | umption      | (Internal c | ell: 0.7 <i>µ</i> V | V/MHz/gat    | e at 3.3 V   | )          |              |             |             |             | 3.3V       | 3.3V     |   |

|                                                           |                 | • Drivab                                                                                          |             |              |             |                     | 5.0 V, IOL   |              |            |              | 3 V,        |             |             | 5.50       | 5.0V     |   |

|                                                           |                 |                                                                                                   | Iol         | = 0.1, 0.5,  | 1, 3, 6 m   | A at 2.5 V          | , IOL = 0.05 | 6, 0.3, 0.6, | 2, 4 mA a  | t 2.0 V)     |             |             |             |            |          |   |

|                                                           | Double layer    | S1L50062                                                                                          | S1L50122    | S1L50282     | S1L50552    | S1L50752            | S1L50992     | S1L51252     | S1L51772   | S1L52502     | S1L53352    | S1L54422    | S1L55062    | S1L56682   | S1L58152 | ! |

| Model                                                     | Triple layer    | S1L50063                                                                                          | S1L50123    | S1L50283     | S1L50553    | S1L50753            | S1L50993     | S1L51253     | S1L51773   | S1L52503     | S1L53353    | S1L54423    | S1L55063    | S1L56683   | S1L58153 |   |

|                                                           | Quadruple layer | S1L50064                                                                                          | S1L50124    | S1L50284     | S1L50554    | S1L50754            | S1L50994     | S1L51254     | S1L51774   | S1L52504     | S1L53354    | S1L54424    | S1L55064    | S1L56684   | S1L58154 | ł |

| Total BC (                                                | Row gates)      | 5.8k                                                                                              | 12.0k       | 28.8k        | 55.5k       | 75.8k               | 99.2k        | 125.8k       | 177.1k     | 250.2k       | 335.9k      | 442.2k      | 506.7k      | 668.6k     | 815.5k   |   |

|                                                           | Double layer    | 2.9k                                                                                              | 6.0k        | 14.4k        | 26.1k       | 35.7k               | 46.7k        | 56.6k        | 79.7k      | 112.6k       | 144.5k      | 176.9k      | 202.7k      | 267.5k     | 326.2k   |   |

|                                                           | Triple layer    | 5.1k                                                                                              | 10.6k       | 25.3k        | 47.2k       | 64.4k               | 84.4k        | 100.7k       | 132.8k     | 187.7k       | 251.9k      | 309.5k      | 354.7k      | 468.0k     | 570.9k   |   |

|                                                           | Quadruple layer | 5.5k                                                                                              | 11.4k       | 27.3k        | 52.8k       | 72.0k               | 94.3k        | 119.5k       | 168.2k     | 237.7k       | 319.1k      | 397.9k      | 456.1k      | 601.7k     | 734.0k   |   |

| Total Load Count                                          | 80 <i>µ</i> m   | -                                                                                                 | 56          | 88           | 124         | 144                 | 168          | 188          | 224        | 264          | 308         | 352         | 376         | 432        | 480      |   |

| Total BC (Re<br>I<br>Total Lead Count<br>Total Lead Count | 70 <i>µ</i> m   | 48                                                                                                | 64          | 104          | 144         | 168                 | 192          | 216          | -          | -            | -           | -           | -           | -          | -        |   |

|                                                           | Internal gates  |                                                                                                   |             | tpd =        | 0.14 ns (   | 3.3 V, F/C          | 0 2, typica  | l wire loa   | d), 0.21 n | s (2.0 V, F  | /O 2, typi  | ical wire l | oad)        |            |          |   |

| Delay Time                                                | Input buffer    | tpd = 0.3                                                                                         | 8 ns (5.0 ) | V, F/O 2, ty | pical wire  | e load) Le          | vel shifter: | 0.4 ns (3.   | 3 V, F/O 2 | , typical w  | vire load), | 1.3 ns (2.  | 0 V, F/O 2, | typical wi | re load) |   |

|                                                           | Output buffer   |                                                                                                   |             |              | tpd = 2.1   | 2 ns (5.0           | V) Level sl  | hifter: 2.0  | 2 ns (3.3  | V), 3.9 ns   | (2.0 V) CI  | L = 15 pF   |             |            |          |   |

| I/O                                                       | level           |                                                                                                   |             |              |             |                     | CMOS         | , LVTTL, F   | PCI-5V, PC | CI-3.3V      |             |             |             |            |          |   |

| Input                                                     | modes           |                                                                                                   |             |              | L           | VTTL, CN            | 10S, Pull-u  |              | wn, Schn   | nitt, Fail-s | afe, Gate   | d           |             |            |          |   |

| Output                                                    | t modes         |                                                                                                   |             |              | N           | ormal, O            | pen drain    | , 3-state,   | Bidirectio | nal, Fail-s  | afe, Gate   | ed          |             |            |          |   |

Note: Figures shown for usable gates are approximations. The actual number of usable gates varies according to the implemented circuitry.

### S1L5V000 Series

|                                                                               |                 |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                    |                    |                   |             |             |          | 4 |  |  |  |

|-------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|-------------------|-------------|-------------|----------|---|--|--|--|

| Se                                                                            | ries            | S1L5V000 se                                                  | eries                                                                                                                                                                                                                                                                                                                                                                                               |                    |                    |                    |                   |             | 5.0V        | 5.0V     | 1 |  |  |  |

| Quadruple laye<br>Total BC (Row gates)<br>Usable<br>gates<br>Total Lead Count |                 | High speed op     Low power co                               | <ul> <li>Large scale integration (0.35 μm CMOS, using 2-, 3-, 4-layer interconnect process)</li> <li>High speed operation (internal gate delay: 0.19ns at 5V, 0.29ns at 3.3V, 2-input power NAND Typ.)</li> <li>Low power consumption (Internal cell: 5V 1.3 μW/MHz/BC, 3.3V 0.54uW/MHz/BC)</li> <li>Drive capacity (loL=0.1, 1, 3, 8, 12, 24mA at 5.0V, IoL=0.1, 1, 2, 6, 10mA at 3.3V)</li> </ul> |                    |                    |                    |                   |             |             |          |   |  |  |  |

| Double laye                                                                   |                 | S1L5V012                                                     | S1L5V042                                                                                                                                                                                                                                                                                                                                                                                            | -                  | S1L5V112           | -                  | S1L5V252          | -           |             | S1L5V482 |   |  |  |  |

| Model                                                                         | Triple layer    | S1L5V013                                                     | S1L5V043                                                                                                                                                                                                                                                                                                                                                                                            | S1X5V513*          | S1L5V113           | S1X5V523*          | S1L5V253          | S1X5V5      | 33*         | S1L5V483 |   |  |  |  |

|                                                                               | Quadruple layer | S1L5V014                                                     | S1L5V044                                                                                                                                                                                                                                                                                                                                                                                            | S1X5V514*          | S1L5V114           | S1X5V524*          | S1L5V254          | S1X5V5      | 34*         | S1L5V484 |   |  |  |  |

| Total BC (                                                                    | Row gates)      | 8.8k                                                         | 42.0k                                                                                                                                                                                                                                                                                                                                                                                               | 26.0k              | 109.2k             | 90.3k              | 254.3k            | 235.0       | k           | 479.9k   |   |  |  |  |

|                                                                               | Double layer    | 2.6k                                                         | 12.6k                                                                                                                                                                                                                                                                                                                                                                                               | -                  | 32.7k              | -                  | 63.5k             | -           |             | 119.9k   |   |  |  |  |

|                                                                               | Triple layer    | 5.3k                                                         | 25.2k                                                                                                                                                                                                                                                                                                                                                                                               | 14.3k              | 65.5k              | 49.7k              | 139.8k            | 129.3       | k           | 239.9k   |   |  |  |  |

| gutes                                                                         | Quadruple layer | 6.1k                                                         | 29.4k                                                                                                                                                                                                                                                                                                                                                                                               | 16.9k              | 76.4k              | 58.7k              | 165.3k            | 152.8       | k           | 287.9k   |   |  |  |  |

| Total Le                                                                      | ad Count        | 48                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                   | 04                 | 10                 | 68                 | 25                | 56          |             | 308      |   |  |  |  |

|                                                                               | Internal Gates  | tpd=0.                                                       | 19ns (5.0V opera                                                                                                                                                                                                                                                                                                                                                                                    | tion, F/O=2, typi  | cal wiring load),  | tpd=0.29ns (3.3V   | operation, F/O=2  | , typical w | viring load | ł)       |   |  |  |  |

| Delay Time                                                                    | Input Buffer    | tpd=                                                         | 0.45ns (5.0V ope                                                                                                                                                                                                                                                                                                                                                                                    | ration, F/O=2, typ | ical wiring load), | tpd=0.55ns (3.3V c | operation, F/O=2, | typical wir | ing load)   |          |   |  |  |  |

| Output Buffer                                                                 |                 |                                                              | tpd=2                                                                                                                                                                                                                                                                                                                                                                                               | .07ns (5.0V oper   | ation, CL=15pF),   | tpd=2.95ns(3.3V    | operation, CL=15  | pF)         |             |          |   |  |  |  |

| I/O                                                                           | level           |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                     |                    | CMOS, TT           | L, LVTTL           |                   |             |             |          |   |  |  |  |

| Input                                                                         | modes           |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                     | TTL, LVTTL, CM     | OS, Pull-up/Pull-o | down, Schmitt, Fa  | ail-safe, Gated   |             |             |          |   |  |  |  |

| Outpu                                                                         | t modes         | Normal, Open-drain, 3-state, Bidirectional, Fail safe, Gated |                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                    |                    |                   |             |             |          |   |  |  |  |

Note: Figures shown for usable gates are approximations. The actual number of usable gates varies according to the implemented circuitry. \*: Analog PLL built in master

Core I/O

|                  |                 |                                                                             |                                   |                   |                            |                  |                  |                |          |          | Core   | I/O      |

|------------------|-----------------|-----------------------------------------------------------------------------|-----------------------------------|-------------------|----------------------------|------------------|------------------|----------------|----------|----------|--------|----------|

| S1L6000          | IL60000 Series  |                                                                             |                                   |                   |                            |                  |                  |                |          | 1.8V     | 1.8V   |          |

| Ser              | ries            | S1L60000                                                                    | S1L60000 Series                   |                   |                            |                  |                  |                |          |          |        | 3.3V     |

|                  |                 | a Liltura Jawa                                                              |                                   |                   | CMOC                       | 2. 4 Januari int |                  |                |          |          | 2.0V   | 2.0V     |

|                  |                 |                                                                             | e scale integra<br>ed operation ( | . ,               |                            |                  |                  |                |          |          |        | 3.3V     |

| Feat             | ures            |                                                                             | er consumptio                     |                   |                            |                  |                  | 21.            | )        |          | 2.5V   | 2.5V     |

|                  |                 | <ul> <li>Drivability</li> </ul>                                             | y (IoL = 0.1, 1,                  |                   |                            |                  | •                |                | <b></b>  |          |        | 3.3V     |

|                  |                 |                                                                             | IOL = 0.05                        | , 0.3, 1, 2, 3, 6 | mA at 2.0 V,               | IOL = 0.045, 0.  | 27, 0.9, 1.8, 2. | 7, 5.4 mA at 1 | .8 V)    |          |        |          |

| Model            | Triple layer    | S1L60093                                                                    | S1L60173                          | S1L60283          | S1L60403                   | S1L60593         | S1L60833         | S1L61233       | S1L61583 | S1I      | _61903 | S1L62513 |

| wodei            | Quadruple layer | S1L60094                                                                    | S1L60174                          | S1L60284          | S1L60404                   | S1L60594         | S1L60834         | S1L61234       | S1L61584 | S1I      | _61904 | S1L62514 |

| Total BC (R      | Row gates)      | 99.2k                                                                       | 171.8k                            | 284.4k            | 400.3k                     | 595.4k           | 831.6k           | 1,234.9k       | 1,587.8k | 1,9      | 903.0k | 2,519.6k |

| Usable           | Triple layer    | 59.6k                                                                       | 103.1k                            | 142.2k            | 200.2k                     | 297.7k           | 332.7k           | 494.0k         | 635.1k   | 635.1k 7 |        | 1,007.9k |

| gates            | Quadruple layer | 69.5k                                                                       | 120.2k                            | 184.9k            | 260.2k                     | 387.0k           | 415.8k           | 617.5k         | 793.9k   | 951.5k   |        | 1,259.8k |

| Total Lead Count | 80 <i>µ</i> m   | —                                                                           | _                                 | _                 | -                          | _                | 284              | 344            | 388      |          | 424    | 488      |

| Total Lead Count | 70 $\mu$ m      | 112                                                                         | 148                               | 188               | 224                        | 272              | -                | -              | -        |          | -      | _        |

|                  | Internal gates  |                                                                             |                                   |                   | t <sub>pd</sub> = 107 ps ( | 2.5 V, F/O 1, †  | typical wire lo  | oad)           |          |          |        |          |

| Delay Time       | Input buffer    |                                                                             |                                   |                   | tpd = 270 ps (2            | 2.5 V, F/O 2, t  | ypical wire lo   | oad)           |          |          |        |          |

| Output buffer    |                 |                                                                             |                                   |                   | t <sub>pd</sub> = 16       | 00 ps (2.5 V,    | CL = 15 pF)      |                |          |          |        |          |

| I/O le           | evels           |                                                                             |                                   |                   | CM                         | OS, LVTTL, P     | CI-3.3V          |                |          |          |        |          |

| Input r          | modes           | CMOS, LVTTL, Pull-up/Pull-down, Schmitt, Level shifter, Fail-safe, Gated    |                                   |                   |                            |                  |                  |                |          |          |        |          |

| Output           | modes           | Normal, Open drain, 3-state, Bidirectional, Level shifter, Fail-safe, Gated |                                   |                   |                            |                  |                  |                |          |          |        |          |

Note: Figures shown for usable gates are approximations. The actual number of usable gates varies according to the implemented circuitry.

9

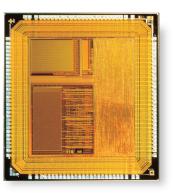

# Gate Arrays

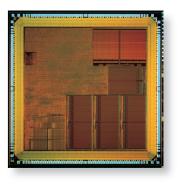

## **Embedded Arrays ASICs**

# **Standard Cells**

Creating hard macros for cells that are highly integrated and have advanced functionality enables development of system-on-a-chip designs, and utilization of the sea-of-gates structure in the logic means that the development period subsequent to the interconnection process is roughly equivalent to that for gate array chips.

In addition, the base array for LSI can be reused allowing only the logic block to be modified in development lead time equivalent to that for gate array chips.

Embedded array technology also facilitates circuit design changes and thereby helps avoid the risks associated with product modifications.

#### S1X5V000 Series

|          |                                                                                                                                                                                                                                                                                                                           | Core | 1/0  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Series   | S1X5V000 Series                                                                                                                                                                                                                                                                                                           | 3.3V | 3.3V |

|          | • High-density integration (0.35 $\mu$ m CMOS process technology and 2/3/4-layer interconnect process)                                                                                                                                                                                                                    | 5.0V | 5.0V |

| Features | <ul> <li>High-speed operation (Internal gate delay: 0.19ns ps/5.0 V, 0.29ns/3.3 V, 2-input power NAND Typ.)</li> <li>Low power consumption (Internal cell: 1.3 µ W/MHz/gate, 5.0V, 0.54 µW/MHz/gate, 3.3V, 2-input NAND T</li> <li>Drivability (IoL=0.1, 1, 3, 8, 12 mA at 5.0 V, 0.1, 1, 2, 6, 10 mA at 3.3 V</li> </ul> | yp.) |      |

#### S1X50000 Series

|          |                                                                                                                                                                    | Core | 1/0  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Series   | S1X50000 Series                                                                                                                                                    | 2.0V | 2.0V |

|          | • High-density integration (0.35 $\mu$ m CMOS process technology and 3/4-layer interconnect process)                                                               | 2.00 | 3.3V |

| _        | High-speed operation (Internal gate delay: 150 ps/3.3 V, 2-input power NAND Typ.)                                                                                  | 2.5V | 2.5V |

| Features | • Low power consumption (Internal cell: $0.37 \mu$ W/MHz/gate, 3.3V, Typ.)                                                                                         | 2.50 | 3.3V |

|          | • Drivability (IoL=0.1, 1, 3, 8, 12, 24 mA at 5.0 V, IoL=0.1, 1, 2, 6, 12 mA at 3.3 V,<br>IoL=0.1, 0.5, 1, 3, 6 mA at 2.5 V, IoL=0.05, 0.3, 0.6, 2, 4 mA at 2.0 V) | 3.3V | 3.3V |

|          |                                                                                                                                                                    | 5.5V |      |

| <br>Core | 1/0  | - |

|----------|------|---|

| 2.0V     | 2.0V |   |

| 2.00     | 3.3V |   |

| 2.5V     | 2.5V |   |

| 2.5V     | 3.3V |   |

| 3.3V     | 3.3V |   |

| 5.5V     | 5.0V | - |

### S1X60000 Series

|          |                                                                                                                                                                                                                                                                                          | l Core | 1/0          |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|

| Series   | S1X60000 Series                                                                                                                                                                                                                                                                          |        | 2.0V         |

|          | <ul> <li>High-density integration (0.25 µm CMOS process technology and 3/4/5-layer interconnect<br/>process, number of raw gates: 2,500,000 Max.)</li> </ul>                                                                                                                             | 2.0V   | 3.3V         |

| Features | <ul> <li>High-speed operation (Internal gate delay: 107 ps/2.5 V, 2-input power NAND Typ.)</li> <li>Low power consumption (Internal cell: 0.18 ⊬W/MHz/gate, 2.5V, Typ.)</li> <li>Drivability (IoL = 0.1, 1, 3, 6, 12, 24 mA at 3.3 V, IoL = 0.1, 1, 3, 6, 12, 24 mA at 2.5 V,</li> </ul> | 2.5V   | 2.5V<br>3.3V |

|          | loL = 0.05, 0.3, 1, 2, 4, 8 mA at 2.0 V)                                                                                                                                                                                                                                                 |        |              |

#### S1X80000 Series

|          |                                                                                                                                                                                                                                                                                                                                    | Core | I/O  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Series   | <ul> <li>S1X80000 Series</li> <li>Based on 0.15 µm CMOS process technology using 4/5-layer interconnect process</li> <li>Internal gate delay: 47.1ps/1.8V, 2-input NAND Typ.</li> <li>Lower power consumption (Internal cell: 0.063 µW /MHz/gate 2-input NAND Typ.)</li> <li>Drive performance (lot=2,4,8,12mA at 3.3V)</li> </ul> | 1.8V | 3.3V |

|          | Based on 0.15 //m CMOS process technology using 1/5-layer interconnect process                                                                                                                                                                                                                                                     | LDO  | 3.3V |

| Features | <ul> <li>Internal gate delay: 47.1ps/1.8V, 2-input NAND Typ.</li> <li>Lower power consumption (Internal cell: 0.063 µW /MHz/gate 2-input NAND Typ.)</li> </ul>                                                                                                                                                                     |      |      |

Standard cells (cell-based ASICs) are semi-custom ICs that enable optimally designed internal logic cells, memories such as ROM and RAM, CPU peripherals, and analog circuits to be implemented all on the same chip. As such, standard cells enable more design flexibility than do gate arrays, offer more advanced functionality and higher integration, and can be developed as a system-on-a-chip optimized for the customer's needs. Such optimization leads to ever more compact, power-conserving devices.

|                                                                                                                                                                              |                                                                                                                                                              | Core  | I/O  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|--|

| S1K60000 Series                                                                                                                                                              |                                                                                                                                                              | 2.0V  | 2.0V |  |

| Series                                                                                                                                                                       | S1K60000 Series                                                                                                                                              | 2.0 V | 3.3V |  |

| Series                                                                                                                                                                       |                                                                                                                                                              | 2.5V  | 2.5V |  |

|                                                                                                                                                                              | <ul> <li>Ultra large scale integration (0.25 μm CMOS, using 3-, 4- or 5-layer interconnect process,<br/>number of raw gates: 3,900,000 Max.)</li> </ul>      | 2.5V  | 3.3V |  |

| Features         • High-speed operation (Internal gate delay: 106ps/2.5V, 2-input NAND Typ.)           • Low power consumption (Internal cell: 0.09 μW/MHz/gate, 2.5V, Typ.) |                                                                                                                                                              |       |      |  |

|                                                                                                                                                                              | <ul> <li>Drivability (IoL = 0.1, 1, 3, 6, 12, 24 mA at 3.3 V, IoL = 0.1, 1, 3, 6, 9, 18 mA at 2.5 V,<br/>IoL = 0.05, 0.3, 1, 2, 3, 6 mA at 2.0 V)</li> </ul> |       |      |  |

|                 |                                                                                                                                                                                                                                                                                                           | Core | I/O  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| S1K80000 Series |                                                                                                                                                                                                                                                                                                           | 1.8V | 3.3V |

| Series          | S1K80000 Series                                                                                                                                                                                                                                                                                           | LDO  | 3.3V |

| Features        | <ul> <li>Based on 0.15 µm CMOS process technology using 4/5-layer interconnect process</li> <li>Internal gate delay: 43.9ps/1.8V, 2-input NAND Typ.</li> <li>Lower power consumption (Internal cell: 0.039 µW /MHz/gate 2-input NAND Typ.)</li> <li>Drive performance (IoL=2,4,8,12mA at 3.3V)</li> </ul> |      |      |

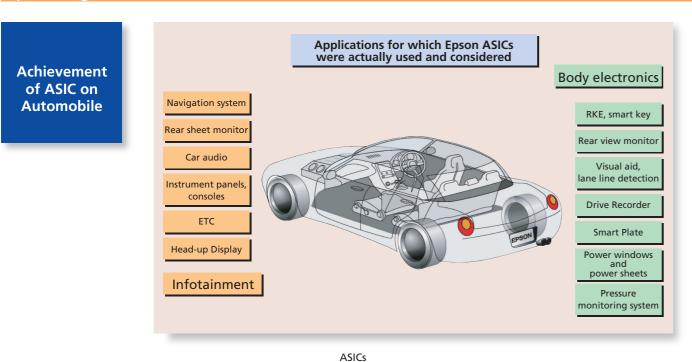

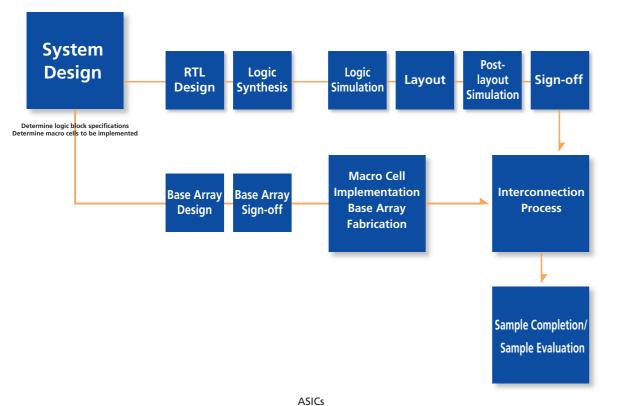

# ASICs

# Macro Cells

### 1. Flash

| Series                   | S1X50000                     |                        | S1X60000/S1K60000*     |

|--------------------------|------------------------------|------------------------|------------------------|

| Operating Voltage        | 2.7 to                       | 3.6V                   | 2.3 to 2.7V            |

| Memory Size              | 64K,128K,256K,512K,1M,2M-bit | 256K,512K,1M,2M,4M-bit | 256K,512K,1M,2M,4M-bit |

| I/O                      | 8,16                         | -bit                   | 16-bit                 |

| Sector Size              | 1Kbyte/sector                | 4Kbyte/sector          | 4Kbyte/sector          |

| Read Access Time (Max.)  | 50ns                         |                        | 50ns                   |

| Operating Current (Max.) | 20mA                         |                        | 20mA                   |

| Standby Current (Max.)   | 10µ                          | A                      | 10µA                   |

| Endurance Time (Max.)    | 1000 c                       | ycles                  | 1000 cycles            |

| Data Retention (Min.)    | 10years                      |                        | 10years                |

| Temperature Range        | 0 to 70 °C                   |                        | 0 to 70 °C             |

| Layer                    | 3                            |                        | 3                      |

\* This macro cell uses the SuperFlash® technologies under license from SST UK Ltd.

### **2. PLL**

| Series                  | S1X5V000        | S1X5            | 0000          |

|-------------------------|-----------------|-----------------|---------------|

| Macro Type              | Macro Type A35M |                 | A35M          |

| Operation Voltage       | 5.0V            | 3.0 to          | 3.6V          |

| Input Frequency         | 5MHz to 40MHz   | 32kHz           | 5MHz to 40MHz |

| Multiplication Ratio    | x2 to x26       | x610 to x4096   | x2 to x26     |

| Output Frequency        | 20MHz to 135MHz | 20MHz to 135MHz |               |

| Period Jitter           | ±2%             | ±3%             | ±2%           |

| Duty                    | 50%±10%         | 50%±            | :10%          |

| Lock Up Time            | 100µs           | 100msec         | 100µs         |

| Low Pass Filter On chip |                 | On chip         |               |

| Temperature Range       | -40 to 110°C    | -40 to 85℃      |               |

| Layer                   | 3               | 3               |               |

| Series               | S1X60000/S1K60000                 |                | S1X80000/S1K80000  |

|----------------------|-----------------------------------|----------------|--------------------|

| Масто Туре           | A25K                              | A25M           | A15M               |

| Operation Voltage    | 2.3 to                            | 2.7V           | 1.65 to 1.95V      |

| Input Frequency      | 32kHz                             | 5MHz to 150MHz | 5MHz to 150MHz     |

| Multiplication Ratio | Max. 16000                        | x1 to x16      | x1 to x16          |

| Output Frequency     | 20MHz to 200MHz                   |                | 20MHz to 200MHz    |

| Period Jitter        | Jitter         ±2%         ±200ps | +20005         | POUT<=100MHz ±2%   |

|                      |                                   | <u>-200</u> ps | POUT>100MHz ±200ps |

| Duty                 | 50%                               | ±5%            | 50%±5%             |

| Lock Up Time         | 100msec                           | 100µs          | 200µs              |

| Low Pass Filter      | On chip                           |                | On chip            |

| Temperature Range    | -40 to 85°C                       |                | -40 to 85℃         |

| Layer                | :                                 | 3              | 3                  |

### 3. SRAM

| Series                     | S1X5V000             |  |

|----------------------------|----------------------|--|

| Масго Туре                 | Standard             |  |

| Port                       | 1-port 2-port (1R+   |  |

| Memory Size/Module         | 128 to 16K-bit       |  |

| Data Bus Width (bit)       | x1 to x32 1-bit step |  |

| Operating Voltage          | 3.3V, 5.0V           |  |

| Operation Frequency (Max.) | 50MHz/5.0V           |  |

| Layer                      | 3                    |  |

| Series                     | S1X50000                |                   |                  |                       |                |                   |

|----------------------------|-------------------------|-------------------|------------------|-----------------------|----------------|-------------------|

| Масго Туре                 | Standard High-Density H |                   | High Speed       |                       |                |                   |

| Port                       | 1-port                  | Dual port (2R+2W) | 1-port           | 1-port                | 2-port (1R+1W) | Dual port (2R+2W) |

| Memory Size/Module         | 128 to 64K-bit          | 1K to 64K-bit     | 32K to 512K-bit  |                       | 32K to 72K-bit |                   |

| Data Bus Width (bit)       | x1 to x32 1-bit step    | x8, x16, x24, x32 | x8, x16, x32     | x1 to x144 1-bit step |                |                   |

| Operating Voltage          | 2.0V, 2.5V,             | 3.0V, 3.3V        | 2.0V, 3.0V, 3.3V | 3.3V                  |                |                   |

| Operation Frequency (Max.) | 71N                     | 1Hz               | 76MHz            | 125MHz 110MHz         |                | MHz               |

| Layer                      | 3                       | 3                 | 3                | 3                     |                |                   |

| Series                     | S1X60000/S1K60000            |                   |                 |           |                |

|----------------------------|------------------------------|-------------------|-----------------|-----------|----------------|

| Macro Type                 | Star                         | ndard             | High-Density    | High      | Speed          |

| Port                       | 1-port                       | Dual port (2R+2W) | 1-port          | 1-port    | 2-port (1R+1W) |

| Memory Size/Module         | 128 to 64K-bit 1K to 64K-bit |                   | 32K to 512K-bit | 128 to    | 64K-bit        |

| Data Bus Width (bit)       | x1 to x32 1-bit step         | x8, x16, x24, x32 | x8, x16, x32    | x4 to x64 | 1-bit step     |

| Operating Voltage          |                              | 2.0V, 2.5V        |                 | 2.        | 5V             |

| Operation Frequency (Max.) | 125MHz                       | 125MHz 119MHz     |                 | 179       | MHz            |

| Layer                      | 3                            |                   | 3               |           | 3              |

| Series                     |                      | S1X80000/S1K80000    |                   |                |  |

|----------------------------|----------------------|----------------------|-------------------|----------------|--|

| Масто Туре                 |                      | Standard             |                   |                |  |

| Port                       | 1-port               | 2-port (1R+1W)       | Dual port (2R+2W) | 1-port         |  |

| Memory Size/Module         | 128 to 64K-bit       | 64 to 16K-bit        | 1K to 32K-bit     | 128K to 1M-bit |  |

| Data Bus Width (bit)       | x1 to x32 1-bit step | x1 to x32 1-bit step | x8, x16, x24, x32 | x8, x16, x32   |  |

| Operating Voltage          |                      | 1.8V                 |                   |                |  |

| Operation Frequency (Max.) | 125MHz               | 119MHz               | 116MHz            | 74MHz          |  |

| Layer                      | 3                    | 4                    | 3                 | 3              |  |

Ask our sales department regarding Gate Array SRAM.

# Macro Cells

#### **Epson Originals -1-** TCON LCD Controller ASICs

- TCON is a display control LSI with a built-in LVDS receiver, suitable for a TFT display module.

- Simply by adding or integrating various dedicated IPs such as LVDS receiver, RSDS transmitter and mini-LVDS transmitter to/with existing display timing control circuits, customers can easily develop TFT display systems in a short period of time, reduce developers' workload, and achieve a faster time to market.

- TCON IPs can be employed on a 0.35-, 0.25- or 0.15µm embedded array/standard cell, providing a developing environment equivalent to ASICs.

|         |                             | 0.35µm Series | 0.25µm Series | 0.18µm Series |

|---------|-----------------------------|---------------|---------------|---------------|

|         | Host interface              |               |               |               |

| TCON IP | 6-/8-bit LVDS receiver      | А             | Α             | A             |

|         | 8-/10-bit LVDS receiver     | —             | _             | Α             |

| Lineup  | Panel interface             |               |               |               |

|         | RSDS transmitter            | А             | Α             | A             |

|         | mini-LVDS transmitter       | —             | Α             | A             |

|         | LVDS transmitter            | —             | А             | Α             |

|         | Image processing IP         |               |               |               |

|         | Overdrive                   | —             | Α             | A             |

|         | γ correction                | —             | Α             | A             |

|         | Contrast correction         | —             | Α             | А             |

|         | Color matrix                | _             | Α             | Α             |

|         | AME(Auto Movie Enhancement) | —             | А             | Α             |

|         | Others                      |               |               |               |

|         | Spread Spectrum IP          | A             | Α             | А             |

|         | Power detection circuit     | А             | Α             | Α             |

|         | Self oscillation circuit    | _             | А             | А             |

A:Available

#### Epson Originals -2- Usable on Automobile

#### Epson Originals -3- Power System Interface

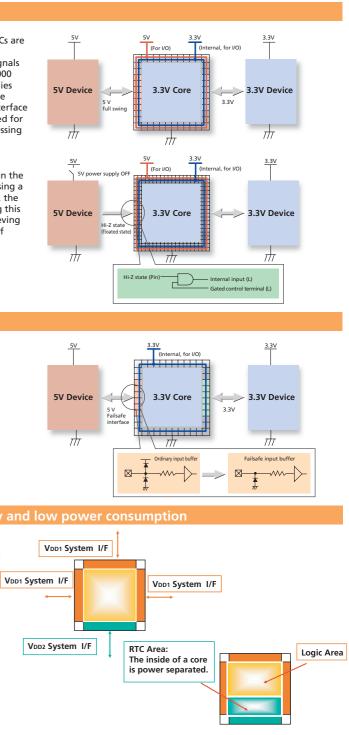

Development of low-voltage system power supplies continues as part of the trend toward reducing power consumption. However, in cases where not all system components can run on a single low-voltage power supply, multiple power supplies are used for the same system. Consequently, many of today's portable electronic devices include dual (5 V/3.3 V) power supplies, each with its own signals.

#### 5 V/3.3 V Dual Power Supply System

| Level Shifter          | Since it is often the case with ASICs that several ICs a connected in the same system, such systems are typically required to handle two types of level signal for 5 V and 3.3 V power. In S1L50000 and S1X50000 series products, the inclusion of two power supplies (such as 5 V and 3.3 V power supplies) enables the implementation of a bilevel (5 V, 3.3 V) signal interfactor each I/O buffer. Such an interface is best suited for applications that include high-speed signal processin and high drive current capacity. |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gated<br>I/O buffer    | The use of the gated input buffer enables input in th<br>Hi-Z state, which has not usually been possible using<br>buffer. In a system using dual-line power supply, the<br>high-voltage power supply may be cut off. Using thi<br>function allows hot-plugging a PC card and achieving<br>lower power consumption in the backup mode of<br>PDA.                                                                                                                                                                                   |

| 3.3 V Single Power     | Supply System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Failsafe<br>I/O Buffer | Even when system constraints preclude the implementation of a dual power supply system, it is still possible to provide an interface between a 3.3 V single power supply chip and a 5 V chip by implementing an input buffer that does not include a forward diode (in the V <sub>DD</sub> direction), which also provides failsafe support for output.                                                                                                                                                                           |

| Power separation s     | uitable for low voltage power supply a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IO Power<br>Separation | <ul> <li>Interface with the devices of other power<br/>systems can be possible by power separation of<br/>I/O cell area.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |

|                        | • When mounted with RTC, power separation<br>between RTC area and Logic area can be<br>possible.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Core Power

Separation

possible Power OFF can be possible in the non RTC area.

# **Epson Originals**

# ASICs Epson Originals

# Package Lineup

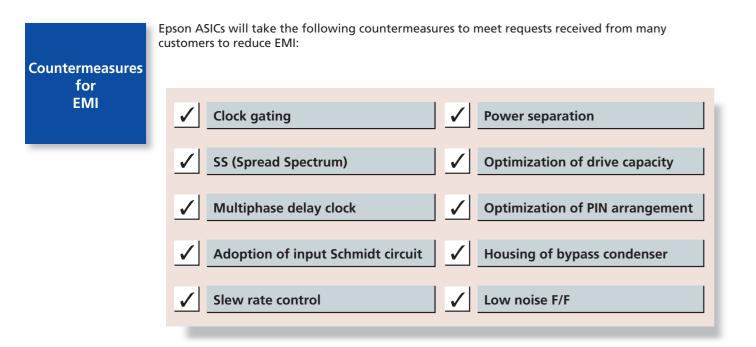

### **Epson Originals -4-** Countermeasures for EMI

## **Epson Originals -5-** Replacement of existing devices For long life time applications.

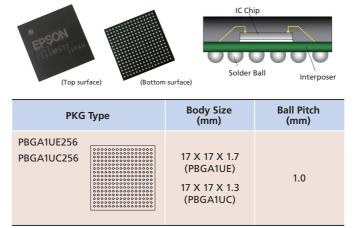

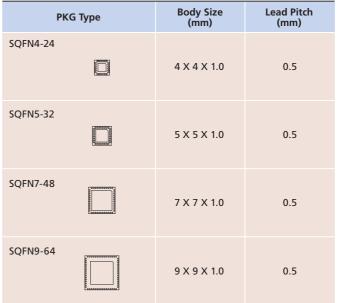

### Plastic Ball Grid Array (PBGA)

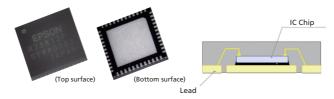

#### Quad Flat Non-leaded Package (QFN)

|   | WCSP                           |                 |                         |                            |

|---|--------------------------------|-----------------|-------------------------|----------------------------|

| 4 | 5012<br>H0402<br>(Top surface) | (Bottom surface | Sdder Ball Over Coat Re | sin Redistribution Circuit |

|   | РКС Туре                       | Pin             | Body Size<br>(mm)       | Ball Pitch<br>(mm)         |

|   | WCSP(S1L5012)                  | 16              | 2.4 X 2.4 X 0.8         | 0.5                        |

|   | WCSP(S1L5028)                  | 25              | 3.0 X 3.0 X 0.8         | 0.5                        |

|   | WCSP(S1L5075)                  | 49              | 4.2 X 4.2 X 0.8         | 0.5                        |

|   | WCSP(S1L5125)                  | 81              | 5.0 X 5.0 X 0.8         | 0.5                        |

|   | WCSP(S1L60093)                 | 49              | 3.0 X 3.0 X 0.8         | 0.4                        |

# **ASICs** Package Externals

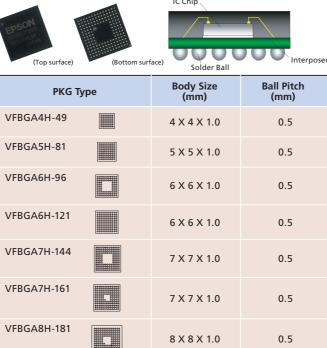

#### Plastic Fine-pitch Ball Grid Array (PFBGA) IC Chip Interposer (Top surface) Solder Ball **Ball Pitch** Body Size РКG Туре (mm) (mm) PFBGA5U-60 5 X 5 X 1.2 0.5 PFBGA5U-81 5 X 5 X 1.2 0.5 PFBGA6U-96 6 X 6 X 1.2 0.5 PFBGA6U-121 6 X 6 X 1.2 0.5 PFBGA7U-144 7 X 7 X 1.2 0.5 PFBGA7U-161 7 X 7 X 1.2 0.5 PFBGA8U-161 8 X 8 X 1.2 0.5 PFBGA8U-181 8 X 8 X 1.2 0.5 PFBGA7U-100 7 X 7 X 1.2 0.65 PFBGA8U-112 8 X 8 X 1.2 0.65 PFBGA8U-121 8 X 8 X 1.2 0.65 PFBGA10U-160 10 X 10 X 1.2 0.65 PFBGA10U-180 10 X 10 X 1.2 0.65 PFBGA12U-208 12 X 12 X 1.2 0.65 PFBGA7U-48 7 X 7 X 1.2 0.8 PFBGA8U-81 8 X 8 X 1.2 0.8 PFBGA10U-121 10 X 10 X 1.2 0.8

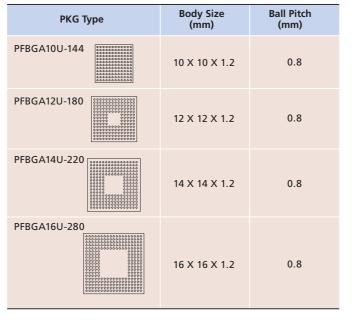

## Very Thin Fine-pitch Ball Grid Array (VFBGA)

10 X 10 X 1.0

10 X 10 X 1.0

10 X 10 X 1.0

0.5

0.8

0.8

# Packag

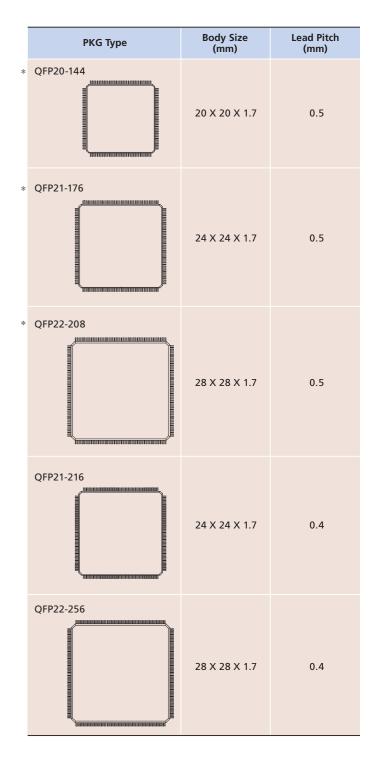

| PI         | КБ Туре | Body Size<br>(mm) | Lead Pitch<br>(mm) |

|------------|---------|-------------------|--------------------|

| TQFP12-48  |         | 7 X 7 X 1.2       | 0.5                |

| QFP12-48   |         | 7 X 7 X 1.7       | 0.5                |

| TQFP13-64  |         | 10 X 10 X 1.2     | 0.5                |

| QFP13-64   |         | 10 X 10 X 1.7     | 0.5                |

| TQFP14-80  |         | 12 X 12 X 1.2     | 0.5                |

| QFP14-80   |         | 12 X 12 X 1.7     | 0.5                |

| TQFP14-100 |         | 12 X 12 X 1.2     | 0.4                |

| TQFP15-100 |         | 14 X 14 X 1.2     | 0.5                |

| QFP15-100  |         | 14 X 14 X 1.7     | 0.5                |

| TQFP15-128 |         | 14 X 14 X 1.2     | 0.4                |

| QFP15-128  |         | 14 X 14 X 1.7     | 0.4                |

\* Can be on automobile

VFBGA10H-240

VFBGA10H-121

VFBGA10H-144

# Package Externals

# Gate Array Package List

Epson's Gate Array Series offers various packages for each base array. Please select the most suitable package, based on the circuit specifications and number of input/output terminals.

Gate Array Package List is subject to change due to the preparation condition of the lead frame and the improvement of production efficiency. Please consult Epson sales office when you are choosing packages.

#### S1L5V000 Series

|      | A      | _2-Series  | S1L5V012 | S1L5V042 | -         | S1L5V112 | -         | S1L5V252 | -         | S1L5V482 |

|------|--------|------------|----------|----------|-----------|----------|-----------|----------|-----------|----------|

|      | A      | _3-Series  | S1L5V013 | S1L5V043 | S1X5V513* | S1L5V113 | S1X5V523* | S1L5V253 | S1X5V533* | S1L5V483 |

|      | A      | _4-Series  | S1L5V014 | S1L5V044 | S1X5V514* | S1L5V114 | S1X5V524* | S1L5V254 | S1X5V534* | S1L5V484 |

|      | R      | aw Gates   | 8.9k     | 42.0k    | 26.0k     | 109.3k   | 90.3k     | 254.4k   | 235.0k    | 479.9k   |

| A    | L2-Usa | ble Gates  | 2.7k     | 12.6k    | -         | 32.8k    | -         | 63.6k    | -         | 119.9k   |

| A    | L3-Usa | ble Gates  | 5.4k     | 25.2k    | 14.3k     | 65.6k    | 49.7k     | 139.9k   | 129.3k    | 239.9k   |

| A    | L4-Usa | ble Gates  | 6.2k     | 29.4k    | 16.9k     | 76.5k    | 58.7k     | 165.4k   | 152.8k    | 287.9k   |

|      |        | Pads       | 48       | 10       | )4        | 16       | 68        | 25       | 56        | 308      |

| PKG  | Pin    | PKG Type   |          |          |           |          |           |          |           |          |

| TQFP | 48     | TQFP12-48  | А        | 1        | A         | 1        | Ą         |          |           |          |

| QFP  | 48     | QFP12-48   | А        | 1        | A         | А        |           |          |           |          |

| TQFP | 64     | TQFP13-64  |          | 1        | A         | А        |           | А        |           | Ν        |

| QFP  | 64     | QFP13-64   |          | 1        | A         | А        |           | А        |           | Ν        |

| TQFP | 80     | TQFP14-80  |          | 1        | А         |          | А         |          |           |          |

| QFP  | 80     | QFP14-80   |          | 1        | А         |          | А         |          | A         |          |

| TQFP | 100    | TQFP14-100 |          | 1        | A         | А        |           | A        |           | Ν        |

| TQFP | 100    | TQFP15-100 |          | 1        | A         | А        |           | А        |           | LQ       |

| QFP  | 100    | QFP15-100  |          | 1        | A         | А        |           | А        |           | LQ       |

| TQFP | 128    | TQFP15-128 |          | A (1     | 04)       | А        |           | 1        | A         | LQ       |

| QFP  | 128    | QFP15-128  |          | A (1     | 04)       | 1        | 4         | 1        | A         | LQ       |

| QFP  | 144    | QFP20-144  |          |          |           | 1        | 4         | 1        | A         | А        |

| QFP  | 176    | QFP21-176  | Ν        | 1        | N         | A (1     | 68)       | 1        | A         | LQ       |

| QFP  | 208    | QFP22-208  | Ν        | 1        | N         | 1        | N         | 1        | Α         | А        |

| QFP  | 216    | QFP21-216  | Ν        | 1        | Ν         |          | N         | 1        | A         | LQ       |

| QFP  | 256    | QFP22-256  | Ν        | 1        | Ν         |          | N         | L        | Q         | LQ       |

| QFN  | 24     | SQFN4-24   | А        | 1        | Ν         |          | Ν         |          | N         |          |

| QFN  | 32     | SQFN5-32   | А        | А        |           | Ν        |           | Ν        |           |          |

| QFN  | 48     | SQFN7-48   | Ν        | А        |           | А        |           | Ν        |           |          |

| QFN  | 64     | SQFN9-64   | Ν        | 1        | 4         | А        |           | А        |           |          |

A: Available for mass production

LQ: Quality assurance required (Lead frame required to be developed)

N: Not available A( ): Usable up to the numbers of pins in the parenthesis

\*: Analog PLL built in master

S1L50000 Series

|      | Al      | _2-Series  | S1L50062 | S1L5 | 0122  | S1L5   | 0282        | S1L5        | 0552        | S1L5   | 0752 | SIL | 50992  | S1L | 51252  | S1L51772    | S1L52502    | S1L53352    | S1L54422    | S1L55062    | S1L56682    | S1L58152    |

|------|---------|------------|----------|------|-------|--------|-------------|-------------|-------------|--------|------|-----|--------|-----|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

|      | Al      | _3-Series  | S1L50063 | S1L5 | 0123  | S1L5   | 0283        | S1L5        | 0553        | S1L5   | 0753 | SIL | 50993  | S1L | 51253  | S1L51773    | S1L52503    | S1L53353    | S1L54423    | S1L55063    | S1L56683    | S1L58153    |

|      | Al      | 4-Series   | S1L50064 | S1L5 | 0124  | S1L5   | 0284        | S1L5        | 0554        | S1L5   | 0754 | SIL | 50994  | S1L | .51254 | S1L51774    | S1L52504    | S1L53354    | S1L54424    | S1L55064    | S1L56684    | S1L58154    |

|      | R       | aw Gates   | 5.8k     | 12   | .0k   | 28     | .8k         | 55          | .5k         | 75     | .8k  | 99  | 9.2k   | 12  | 25.8k  | 177.1k      | 250.2k      | 335.9k      | 442.2k      | 506.7k      | 668.6k      | 815.5k      |

| AL   | L2-Usal | ble Gates  | 2.9k     | 6.   | Ok    | 14     | .4k         | 26          | 6.1k        | 35     | .7k  | 46  | 6.7k   | 5   | 6.6k   | 79.7k       | 112.6k      | 144.5k      | 176.9k      | 202.7k      | 267.5k      | 326.2k      |

| AL   | _3-Usal | ble Gates  | 5.1k     | 10   | .6k   | 25     | i.3k        | 47          | '.2k        | 64     | .4k  | 84  | 1.4k   | 10  | 00.7k  | 132.8k      | 187.7k      | 251.9k      | 309.5k      | 354.7k      | 468.0k      | 570.9k      |

| AL   | _4-Usal | ble Gates  | 5.5k     | 11   | .4k   | 27     | '.3k        | 52          | .8k         | 72     | .0k  | 94  | 1.3k   | 11  | 19.5k  | 168.2k      | 237.7k      | 319.1k      | 397.9k      | 456.1k      | 601.7k      | 734.0k      |

|      |         | Pads       | 48       | 64   | 56    | 104    | 88          | 144         | 124         | 168    | 144  | 192 | 168    | 216 | 6 188  | 224         | 264         | 308         | 352         | 376         | 432         | 480         |

|      | F       | Pad Pitch  | $70\mu$  | 70µ  | 80µ   | 70μ    | 80 <i>µ</i> | 70 <i>µ</i> | 80 <i>µ</i> | 70µ    | 80µ  | 70µ | ι 80 μ | 70, | μ80μ   | 80 <i>µ</i> |

| PKG  | Pin     | PKG Type   |          |      |       |        |             |             |             |        |      |     |        |     |        |             |             |             |             |             |             |             |

| TQFP | 48      | TQFP12-48  | А        | А    | А     |        | А           | А           | А           |        | А    |     | Ν      |     |        |             |             |             |             |             |             |             |

| QFP  | 48      | QFP12-48   | А        | А    | А     |        | А           | А           | А           |        | А    |     | А      |     | Ν      |             |             |             |             |             |             |             |

| TQFP | 64      | TQFP13-64  |          | А    | А     |        | А           | А           | А           |        | А    |     | А      |     | А      | А           | LQ          | Ν           | Ν           |             |             |             |